台积电3nm大揭秘

在对更小、能效更高的晶体管的不懈追求中,半导体行业遇到了更大的挑战,最近的尖端工艺节点将这些挑战推到了最前沿。

台积电的最新节点是其 3 纳米“N3”工艺技术系列。台积电最初计划在 2022 年下半年量产,最终于2022年12月29日在其Fab 18举行了 3 纳米量产和产能扩张仪式。

台积电正在推出多种“3nm”版本。两种主要类型是基本 N3 节点 (N3B) 和增强型 N3 节点 (N3E)。

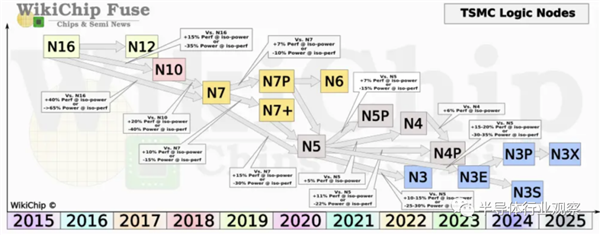

最近,在他们的 2023 年技术研讨会上,该公司还宣布了一些额外的衍生节点。然而,尽管它们的名字相似,但两者并不相关,但遵循截然不同的设计规则。

我们将它们视为两个独立的血统,台积电还计划稍后推出一些性能更高的 N3E 变体。

在第 68 届年度 IEEE 国际电子器件会议 (IEDM) 上,台积电提交了多篇论文——其中两篇是关于他们的 N3 节点。

第二篇论文实际上是一篇“late-news submission”。虽然没有在论文中明确说明,但我们确实与作者确认,第一篇论文指的是 N3B,而第二篇论文是他们的 N3E 节点。

在上个月举行的台积电 2023 技术研讨会上,台积电披露了一些此前未披露的额外细节。

N3B

台积电首个3纳米级工艺技术——N3B最近已经进入量产。尽管台积电延续了其最近的传统,即披露了关于其工艺的极少实际细节,但这篇论文无疑比几年前的 N5 论文要好。

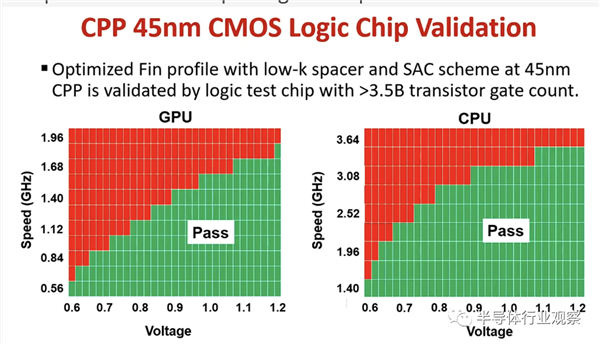

台积电在这里透露,该节点具有 45 纳米的接触栅极间距,这是迄今为止所有代工厂报告的最窄间距。

值得指出的是,从历史上看,台积电在其标准单元实施中依赖稍微宽松一些的 CPP。这使得 N3B 在实际实施中与 CPP 的距离为 45-47 nm。

台积电在其 N3B 节点中引入的其中一件事是一种新的自对准接触 (SAC:self-aligned contact) 方案。这让我们感到惊讶,因为我们认为他们现在已经推出了它。

相比之下,英特尔早在 2011 年就在其 22 纳米工艺中引入了 SAC 以及其 FinFET 晶体管架构。三星也在其 7 纳米系列中引入了 SAC。

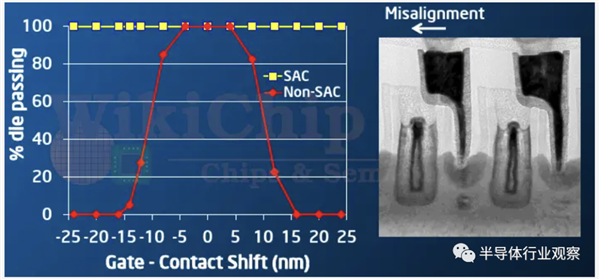

工艺工程师在缩小晶体管时面临的众多挑战之一是由于未对准造成的变化。在现代节点上,由于接触着陆面积(contact landing area)较小,未对准的余量会显著下降,从而影响良率。

除了触点到栅极(contact-to-gate)短路之外,还会出现寄生电容和性能问题。为了缓解这个问题,台积电表示,对于他们的 N3B 及更高版本,他们必须引入 SAC。SAC严格来说是一种提高良率的流程,可防止栅极因前沿工艺节点中的紧密间距而发生接触短路。

在 SAC 下,栅极通过栅极顶部的电介质硬掩模(dielectric hard mask)防止短路。它还允许触点充分利用与垫片(spacers)相邻的空间。最终产品是一个工艺流程,在工艺变化方面更加宽容。

值得注意的是,由于在未对准的情况下接近接触,该过程确实会导致电容恶化。

下图来自台积电,显示了 SAC 如何成功抑制接触到栅极泄漏。与非 SAC 变化相比,在任一方向上最多 3 纳米显示对泄漏的影响最小。

台积电还报告称,与传统接触方案相比,SAC 可将电阻降低 45%,并将变化降低 50%。

顺便说一下,台积电 3 nm 的结果与 2012 年英特尔的 22 nm 非常相似。下面是英特尔在其 22 nm 节点上的 SAC 图表略有不同,它显示了高达 5 nm 的错位公差,100% 的裸片通过.

台积电还谈到了间隔工程(spacer engineering)。随着间隔物(spacer)厚度的增加和接触距离的减小,接触电阻急剧增加。因此,减小间隔物厚度对于将电阻保持在可接受的公差范围内至关重要。

它通过降低栅极电容到鳍片的源极/漏极区域并在顶部接触来实现。虽然更需要更薄的间隔物,但它们难以实施,因为它会对器件的产量和可靠性产生不利影响(对于 FinFET 器件尤其如此)。

为此,台积电表示已确定并实施了适合量产的 K 值 < 4.0 的low-K 间隔器。在他们的 N3B 工艺中,台积电报告说,在通过 TDDB 规范的同时,与之前的间隔物实现相比,Vmax 提高了高达 230 mV。

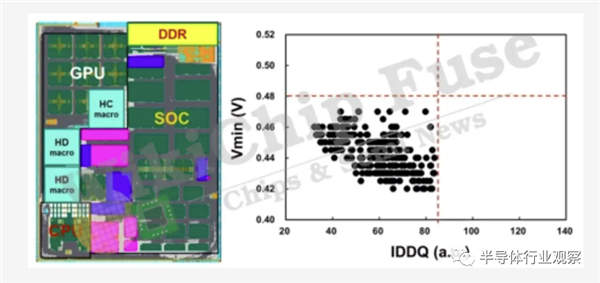

同样的测试芯片还集成了256 Mib的HC和HD SRAM宏。

N3E

N3E 节点是台积电计划在今年下半年推出的一个完全不同的工艺节点,大约在 N3B 推出一年后。对于大多数客户来说,这将是真正N3 节点。这个节点的一切都与 N3B 不同。

为此,N3E 节点提供了 48 纳米的多晶硅间距(poly pitch)、26 纳米的鳍状间距( fin pitch)以及 23 纳米的最小金属间距(metal pitch)。这分别表示 0.94 倍和 0.93 倍的缩放比例。

为了促进 23 nm pitch的最小金属间距,台积电表示它采用了“用于 Cu 的创新衬里”(innovative liner for Cu),以便将标称金属宽度的 RC 降低 20%,对于 2 倍金属宽度降低 RC 多达 30%。

同样,台积电表示,“创新的阻挡工艺”(innovative barrier process)被用来将 Via RC 减少多达 60%。相比之下,英特尔使用的是增强型铜 (eCu:enhanced Copper),它包含一个钽阻挡层,钴包层围绕着一个纯铜核心。

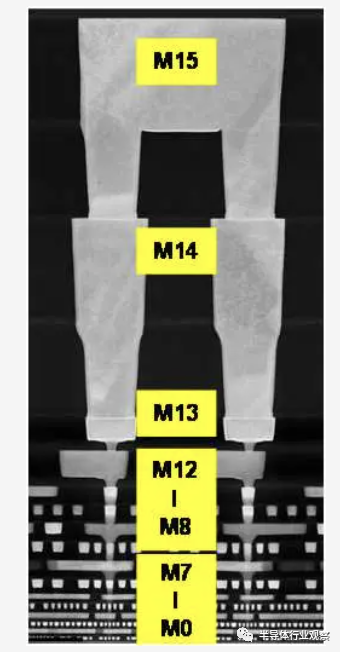

在具有更松弛间距(relaxed pitches)的上层金属层,据说势垒厚度(barrier thickness)已经减少,并且使用极低low-κ 电介质来最小化整体 BEOL RC 延迟。

简要提到了一些额外的制程特征。这是第 6 代high-K 替代金属栅极工艺。台积电表示,对于这一制程,它已经改进了垫片工程(spacer engineering),这似乎与 N3B 所详述的相似。

台积电还提到使用带有双外延工艺的凸起源极/漏极,该工艺针对沟道应变进行了优化,以降低源极/漏极电阻。

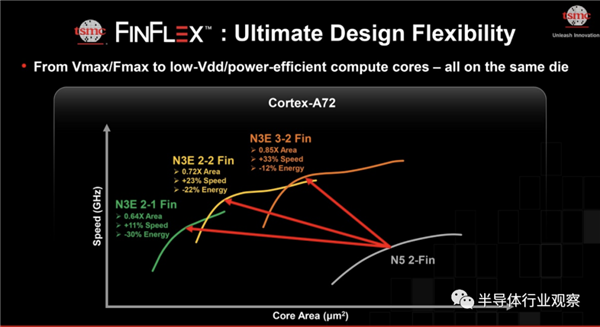

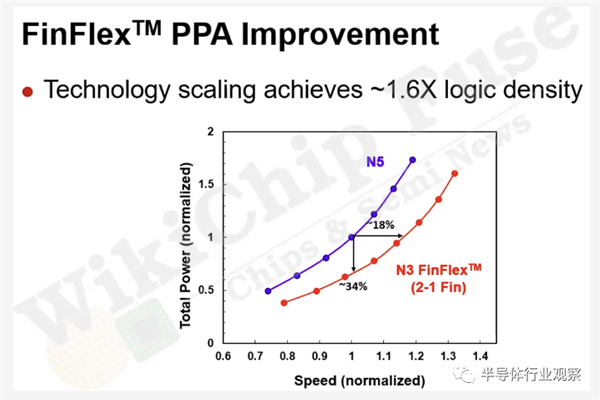

台积电 N3E IEDM 论文的一大焦点是“FinFlex”(hybrid cells),该公司将其描述为“an innovative standard cell architecture with different fin configurations”。

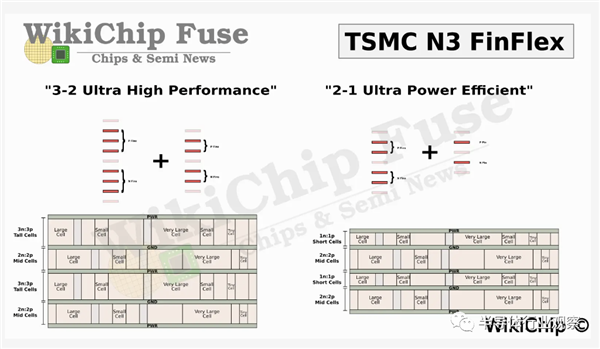

与往常一样,台积电开发了三个主要的逻辑标准单元库——短高度、中高度和分别包含 1、2 和 3 个鳍片高度单元的高标准单元库。

除了独立的应用程序之外,FinFlex 还提供三种预定义的配置,将这些库混合在一起以提供各种密度-性能权衡。

在某种程度上,FinFlex 可以被认为是一个固定的双高标准单元,但台积电确实以一种巧妙的方式将它们结合起来,以在需要的地方利用更高的性能,在性能不是必需的地方利用更高的密度。

所有三个 FinFlex 变体都使用中等高度的 2 fin标准单元。台积电表示,之所以选择它,是因为它具有最佳的性能密度平衡。当与 1 fin库(称为“2-1 fin配置”)结合使用时,台积电表示它可以在不牺牲功耗敏感应用程序性能的情况下实现良好的面积减少。

在这里,混合设置中的 2 fin器件可用于关键路径以利用更高的电流,而单鳍式(fin)单元则用于减少泄漏。

台积电表示,这可以生产迄今为止密度最高的混合标准单元,同时提供最低的功耗。同样,当与 3 fin库(称为“3-2 fin配置”)结合使用时,三fin单元可用于为高性能应用提供更高的驱动电流。

台积电指出,借助hybrid cells FinFlex 配置,通过协同优化 BEOL 布局布线,可实现额外的cell-level 和chip-level 电容降低。

综合起来,N3E 单元高度基于 26 纳米扩散线(diffusion lines)。因此,对于 48 纳米 CPP 的 1、2 和 3 fin cell,我们有 4.5、5.5 和 6.5 扩散线高度,在 54 纳米 CPP 上有 6.5、7.5 和 8.5 线高。

这转化为 48 nm CPP 处的 143 纳米高密度单元高度和 54 nm CPP 处的 195 纳米高密度单元高度。

48 纳米 CPP 的 2-2 配置提供 286 纳米hybrid cells以及 54 纳米多晶硅的 390 纳米。对于 2-2、2-1 和 2-3,这分别在 48 nm CPP 处达到 286 nm、403 nm 和 455 nm,在 54 nm CPP 处达到 390 nm、559 nm 和 611 nm。

请注意,这说明了在混合配置中必须连接的额外 H143/H195。

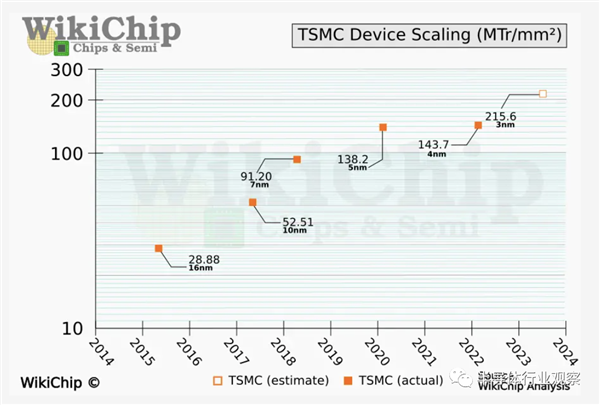

在 48 纳米 CPP 下,143 纳米 HD 单元的晶体管密度约为 215.6 MTr/mm?。

这相当于纯逻辑密度的晶体管缩放比例约为 1.56 倍(没有内置模拟/SRAM,尽管这些在该节点中基本没有变化),这与台积电公布的基于 0.5[Logic]+ 的 1.6 倍逻辑密度数字相对接近0.3[SRAM]+.2[模拟] 利用 2-1 fin配置。

在 48 纳米 CPP 下,169 纳米 HP cell的工作效率约为 182.5 MTr/mm2。具有 54 纳米 CPP 的 3 纳米高性能单元 (H221) 产生的晶体管密度约为 124.02 MTr/mm2。

从历史上看,我们只见过与relaxed poly pitch一起使用的高密度单元。也就是说,221 纳米单元的密度恰好与 Intel 4 HP 单元非常相似。两者显示在下图中以进行比较。

在 2-2、2-1 和 2-3 的上下文中,密度将根据所选配置计算为这些密度的平均值。在 PPA 方面,据说与 2-2 配置相比,3-2 配置比 N5 2-fin 提供 10% 的额外性能,同时面积减少为 2-2 配置的一半。

同样,据说 2-1 配置与 N5 2 fin相比,2-2 配置的面积减少了 8%,同时性能提高了一半。

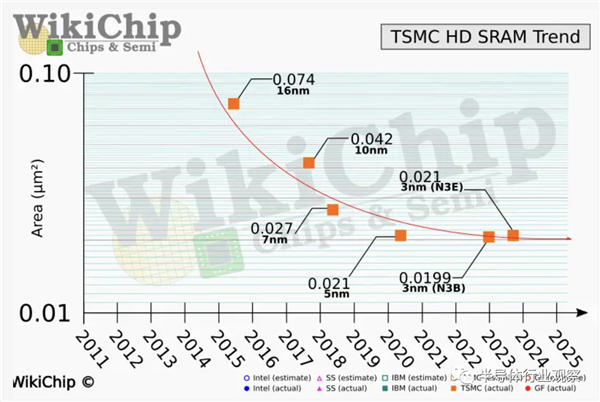

静态随机存取存储器

密度故事中一个有趣的转折点是 SRAM。我们在之前分享了一篇关于SRAM 缩减终止的文章《我们将见证SRAM的死亡》。这里的底线是 SRAM 并没有在 3 纳米上缩小,同时它在绝对面积和总晶体管计数比率方面都占了芯片的更大部分。

SRAM 是芯片设计人员用来提高性能的一个非常重要的杠杆,主要是通过缓存。

当台积电首次宣布 N3E 时,它忽略了 SRAM 密度的改进。我们现在知道 N3E SRAM 位单元与 N5 相同。这对芯片设计师来说是一场灾难。N3B 的表现也好不到哪儿去。

台积电最初透露,N3B SRAM 密度是 N5 的 1.2 倍。IEDM 最近的一项披露显示,它实际上只增加了 5% 的密度。N3B 显着更高的价格很难证明增加的密度和 SRAM 改进很少。

PPACT

最近的工艺节点变得越来越复杂,有上千个步骤。除了一丝不苟的执行,流程设计本身还需要仔细考虑风险与回报的计算。N3B 显然旨在成为 N5 的重大进步;然而,这一进步是以相当大的代价和上市时间延长为代价的。

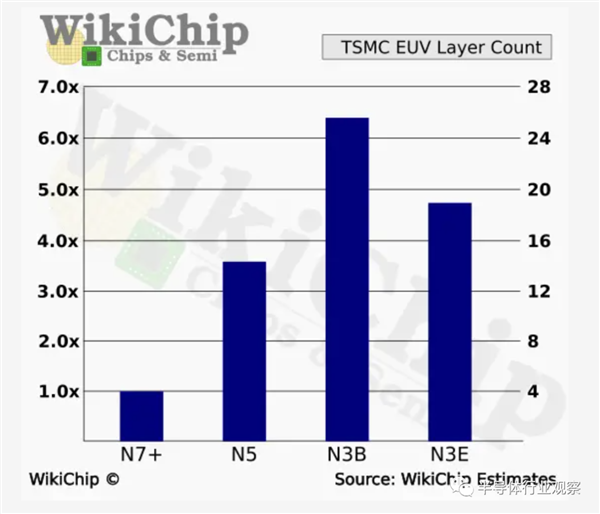

在光刻层面,我们估计 N3B 已将 EUV 层数增加到 25。这代表了近 80% 的惊人增长。这意味着曝光量、光刻总周期时间和最终成本增加了 80%。

值得注意的是,N5 本身的 EUV 层数是 N7+ 的三倍。显然,即使对于另一个节点,这种趋势也不可持续。

N3B 还引入了SAC。这对我来说真的很奇怪,特别是因为它不存在于 N3E 中。这意味着触点最初可能是双重图案化——表明 N3B 可能超过 26 个 EUV 层——但在 SAC 启用下减少到 25 个。更宽松的 N3E 间距可能让他们在没有 SAC 的情况下逃脱,从而进一步降低成本。N2 将来肯定会使用 SAC。

N3E 在扭转 N3B 成本方面迈出了一大步。台积电表示,以前需要双重图案化的三个关键层被单一 EUV 图案化所取代。

我们认为这意味着总共消除了 6 条线和过孔层曝光。这使得估计的层数为 19。这表明 N3E 的内在成本增加了 36%,这是更容易接受的。

在 N3 中做出的许多决定可能已经进入台积电未来的 N2 节点。我们认为,与 N3B 相比,N2 中的 EUV 层将以非常温和的速度增加,考虑到 N2 将提供新的设备架构,这种可能性要大得多。

本站所有文章、数据、图片均来自互联网,一切版权均归源网站或源作者所有。

如果侵犯了你的权益请来信告知我们删除。邮箱:business@qudong.com